## Advanced Design System 2002 RFIC Dynamic Link

February 2002

#### Notice

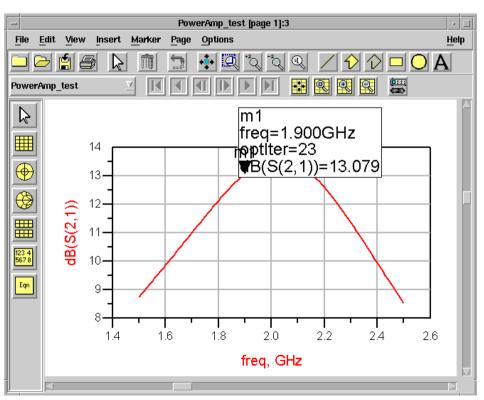

The information contained in this document is subject to change without notice.

Agilent Technologies makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Agilent Technologies shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

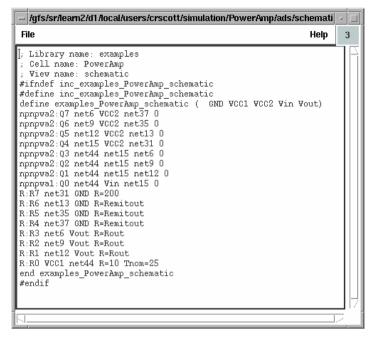

#### Warranty

A copy of the specific warranty terms that apply to this software product is available upon request from your Agilent Technologies representative.

#### **Restricted Rights Legend**

Use, duplication or disclosure by the U. S. Government is subject to restrictions as set forth in subparagraph (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013 for DoD agencies, and subparagraphs (c) (1) and (c) (2) of the Commercial Computer Software Restricted Rights clause at FAR 52.227-19 for other agencies.

Agilent Technologies 395 Page Mill Road Palo Alto, CA 94304 U.S.A.

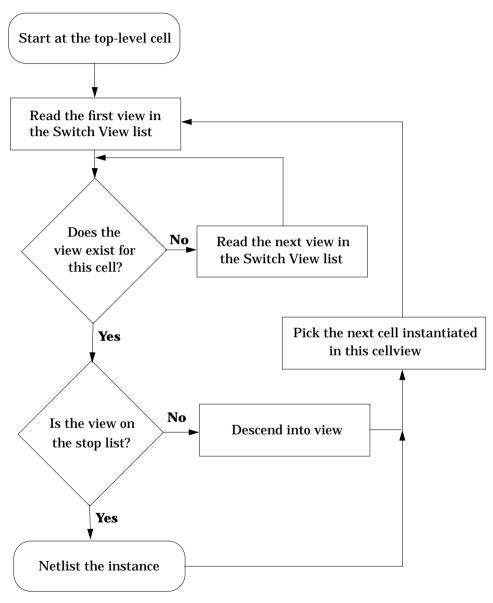

Copyright © 2002, Agilent Technologies. All Rights Reserved.

#### Acknowledgments

Cadence<sup>®</sup> and Analog Artist<sup>®</sup> are registered trademarks of Cadence Design Systems Incorporated.

Design Framework  $II^{\rm TM}$  and Composer  $^{\rm TM}$  are trademarks of Cadence Design Systems Incorporated.

Copyright © 2001 Cadence Design Systems Incorporated. All rights reserved.

## Contents

| 1 | Introduction                                                |      |

|---|-------------------------------------------------------------|------|

|   | Advanced Design System                                      | 1-1  |

|   | Virtuoso Schematic Composer                                 |      |

|   | RFIC Dynamic Link                                           |      |

|   | RFIC Dynamic Link Use Model                                 |      |

|   | What's in this Manual                                       | 1-3  |

| 2 | Administrative Tasks                                        |      |

|   | System Requirements                                         | 2-1  |

|   | Hardware Requirements                                       |      |

|   | Software Requirements                                       |      |

|   | License Requirements                                        |      |

|   | Installing RFIC Dynamic Link                                |      |

|   | Configuring the Cadence Install Directory                   |      |

|   | Running the idfConfigCadence Script                         |      |

|   | Configuring for a New Cadence Release                       |      |

|   | Configuring the Software                                    |      |

|   | Configuring the UNIX Environment                            |      |

|   | Configuring the ADS Install Directory                       |      |

|   | Modifying the RFIC Dyanmic Link-Cadence Initialization File |      |

|   | Modifying the Configuration File                            |      |

|   | Modifying the BindKey Settings                              | 2-12 |

|   | Managing Projects and Designs                               | 2-12 |

| 3 | Getting Started Tutorial                                    |      |

| - | Setting up the Examples Directory                           | 3-1  |

|   | Starting the Cadence Design Framework                       |      |

|   | Opening a Cadence Composer Schematic                        |      |

|   | Linking with Advanced Design System                         |      |

|   | Opening a Test Schematic Design                             |      |

|   | Adding a Symbol of the Cadence Cellview                     |      |

|   | Adding Design Variables                                     |      |

|   | Adding Model Files                                          |      |

|   | Performing a DC Simulation                                  |      |

|   | Annotating DC Operating Points to a Selected Cellview       |      |

|   | Node Probing with RFIC Dynamic Link                         |      |

|   | Performing an S-parameter Simulation                        |      |

|   | Displaying Your Results                                     |      |

|   | Performing a Parameter Optimization                         |      |

|   | Verifying Your Results                                      |      |

|   |                                                             |      |

|   | Ending the Session                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-33                                                              |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| 4 | Starting, Viewing Designs and Exiting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                   |

|   | Starting Advanced Design System<br>Adding an Instance of a Cadence Design<br>Pushing into the Design Hierarchy<br>Exiting                                                                                                                                                                                                                                                                                                                                                                                                 | 4-2<br>4-3                                                        |

| 5 | Netlisting, Simulating, and Displaying Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |

| 5 | Netlisting and Simulating a Design<br>Viewing Netlists<br>Viewing Netlists from Advanced Design System<br>Viewing Netlists from the Cadence Schematic Window<br>Net and Instance Name Mapping<br>Expression Name Mapping<br>Using Global Nodes                                                                                                                                                                                                                                                                            | 5-1<br>5-1<br>5-2<br>5-3<br>5-4                                   |

| 6 | Using Design Variables<br>Adding and Editing Design Variables<br>Updating Cadence Design Variables                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                   |

| 7 | Tuning and Optimizing Designs         Tuning Cadence Instance Parameters and Design Variables         A Dynamic Link For Cadence Tuning Example         Optimizing Designs         Updating the Cadence Cellview                                                                                                                                                                                                                                                                                                          | 7-1<br>7-8                                                        |

| 8 | Annotating a DC Solution<br>Annotating DC Voltages to a Cadence Cellview<br>Annotating DC Currents to a Cadence Cellview<br>Displaying Voltages or Currents from a Previous Simulation<br>Creating Symbols for Hierarchical Subcircuits with cdsTerm                                                                                                                                                                                                                                                                      | 8-2<br>8-5                                                        |

| 9 | Using Additional Features of RFIC Dynamic Link Using the Netlist File Include Component Adding a Netlist File Include Component Accessing the Netlist File Include Dialog Summarizing the Netlist File Include Component Freezing Selected Subcircuits Setting the Freeze Parameter Generating a Cadence Subcircuit Netlist. Setting the netlistFile Parameter Using "Freeze" Mode to Simulate a Design in ADS Standalone Compatibility between Advanced Design System and Cadence Tools. Support for Duplicate Pin Names | 9-1<br>9-2<br>9-9<br>9-10<br>9-10<br>9-11<br>9-12<br>9-12<br>9-13 |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                   |

|    | Using Buses<br>Setting up Unnamed Nets<br>Support for pPar and iPar<br>Using Inherited Connections<br>Using S-parameter File Devices from analogLib                                                   | 9-14<br>9-14<br>9-20     |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 10 | Using Switch Views, Stop Views and the Hierarchy Editor<br>Expanding Hierarchy with the Dynamic Link Netlister<br>Using the Hierarchy Editor with RFIC Dynamic Link<br>Placing the config view in ADS | 10-10                    |

|    | Command Reference and Troubleshooting<br>Cadence Menu<br>ArtistUtilities Menu<br>ADS Menu<br>Troubleshooting<br>Known Problems and Solutions.<br>Installation and Use Checklist                       | A-3<br>A-4<br>A-4<br>A-4 |

# **Chapter 1: Introduction**

Agilent Technologies and Cadence Design Systems both offer powerful EDA design tools. Many of today's design engineers prefer to use a combination of these tools to take advantage of the strengths of both design environments. Because of this desire to use multiple tools, Agilent Technologies has developed the *RFIC Dynamic Link for Cadence.* The Dynamic Link enables both *tops-down* and *bottoms-up* design and simulation in Advanced Design System (ADS) using IC designs from the Cadence database.

### **Advanced Design System**

Advanced Design System has been developed specifically to simulate the entire communications signal path. This unique solution integrates the widest variety of proven RF, DSP, and electromagnetic design tools into a single, flexible environment. Building on years of expertise developing new technologies for our EDA tools, such as Series IV and MDS, Advanced Design System provides a broad range of high-performance capability. This makes it easy to explore design ideas, then model the electrical and physical design of the best candidates.

### Virtuoso Schematic Composer

The Virtuoso Schematic Composer from Cadence Design Systems is a hierarchical design entry tool used by RFIC circuit designers. Useful for both analog and digital designs, the database created is accessible by the Cadence simulation and physical layout tools. The tool supports multi-sheet schematics, including cross-referencing, symbol creation, automatic HDL cell template generation, global nets and hierarchical property definition for most database objects. The tool also provides hierarchical checking of connectivity, consistency of different cell representations and label attachments.

## **RFIC Dynamic Link**

RFIC Dynamic Link is an EDA framework integration software product based on Inter-Process Communication (IPC), rather than data file translation, maximizing data integrity and ease of use. This manual describes how to install and configure the RFIC Dynamic Link product and assists you in designing and analyzing analog mixed-signal and RF circuits via Dynamic Link. Chapter 3, Getting Started Tutorial is provided to help you quickly get started with using the RFIC Dynamic Link. For information on Library Customization, refer to the *RFIC Dynamic Link Library Guide*.

#### **RFIC Dynamic Link Use Model**

The RFIC Dynamic Link use-model coincides with that of both Cadence and ADS, with only a few exceptions. Essentially, the *Affirma Analog Circuit Design Environment (Analog Artist* in 4.4.3) user interface is replaced with the Advanced Design System and all of its functionality. The Affirma features that are not directly replaced by ADS are provided on the *ArtistUtilities* pull-down menu in the Cadence Virtuoso Schematic window.

**Note** If the *ArtistUtilities* pull-down menu does not appear in the Cadence Virtuoso Schematic window, choose **Tools > ADS** in the Cadence schematic window.

Usage assumes basic familiarity with the Cadence *IC Design Framework II (DFII)*, including *Virtuoso* schematic capture and *Affirma Analog Circuit Design Environment*, as well as basic familiarity with design and simulation in the Advanced Design System.

#### **Additional Information**

- Wherever a shell variable is set, this manual uses the K-shell syntax.

- Unless otherwise mentioned, assume case sensitivity.

- Terminology used for Agilent Technologies and Cadence EDA Tools is frequently different. For example, a *project* in ADS is similar to a *library* in Cadence and *design* in ADS is similar to a *cellview* in Cadence.

### What's in this Manual

The goal of this manual is to help you get started, providing relevant examples that teach you how to use the software, and show you where you can get more information as you need it. This manual contains:

- Chapter 2, Administrative Tasks describes the system requirements and how to install and configure the software.

- Chapter 3, Getting Started Tutorial steps you through the process of simulating a circuit using components from the Dynamic Link analogLib library. Other examples are also included to help you become more familiar with the product.

- Chapter 4, Starting, Viewing Designs and Exiting provides information on launching ADS from a Cadence Schematic window, performing some basic operations and closing the Dynamic Link between ADS and Cadence.

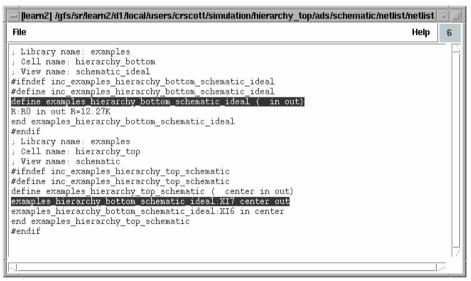

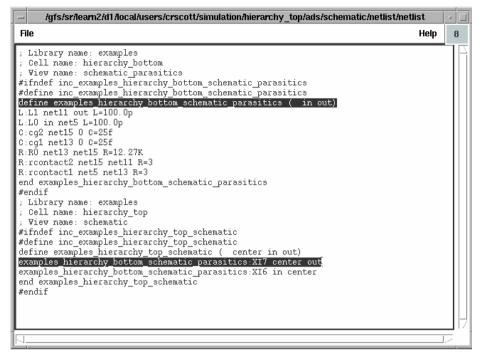

- Chapter 5, Netlisting, Simulating, and Displaying Data describes the procedures for netlisting and simulating a design as well as viewing the netlist from either ADS or a Cadence schematic window. Information on net, instance and expression name mapping is also provided.

- Chapter 6, Using Design Variables describes how to edit a design variable in ADS and also update your Cadence design variables.

- Chapter 7, Tuning and Optimizing Designs provides information on tuning and optimizing designs using the ADS tuning and optimization capabilities.

- Chapter 8, Annotating a DC Solution describes the steps necessary for annotating ADS DC and Operating Point simulation results to the Cadence schematic design.

- Chapter 9, Using Additional Features of RFIC Dynamic Link includes a collection of Dynamic Link features such as using the Netlist File Include component and "Freezing" selective subcircuits. Compatibility features covering support for Duplicate Pin Names, Bus-ports, Buses and Bundles, Unnamed Nets and pPar and iPar are also discussed.

- Chapter 10, Using Switch Views, Stop Views and the Hierarchy Editor provides information on using switch views, stop views and the Hierarchy Editor in Dynamic Link.

- Appendix A, Command Reference and Troubleshooting describes the function of each of the menu selections provided in Advanced Design System (Cadence Menu), Cadence Schematic window (ArtistUtilities Menu), and the Cadence

CIW (ADS Menu) while using the RFIC Dynamic Link. Troubleshooting information that can help you resolve common problems is also provided in this appendix.

# **Chapter 2: Administrative Tasks**

This chapter describes system requirements and how to install and configure the software. You may require help from a UNIX or EDA Administrator to complete these tasks.

### **System Requirements**

This section describes the minimum hardware, operating system, EDA Framework and License requirements necessary for using the RFIC Dynamic Link.

#### **Hardware Requirements**

The information in Table 2-1 describes the *minimum* hardware requirements for the RFIC Dynamic Link.

| Hardware        | Requirement                         |

|-----------------|-------------------------------------|

| RAM             | 256MB                               |

| Swap Space      | 500MB                               |

| Hard Disk Space | 20MB of disk space for installation |

Table 2-1. Dynamic Link Minimum Hardware Requirements

#### **Software Requirements**

RFIC Dynamic Link version 2002 requires ADS 2002. Dynamic Link is supported by Cadence DFII versions 4.4.3QSR1, 4.4.5 and 4.4.6 and on all UNIX operating system versions from Hewlett Packard, Sun and IBM which run this Cadence software. Refer to Table 2-2 for a summary of supported platforms. For additional information, please contact Cadence Design Systems Inc.

| Cadence<br>DFII<br>Version | AIX 4.4.3 | HPUX 10 | HPUX 11 | SUN 56 | SUN 57 | SUN 58 |

|----------------------------|-----------|---------|---------|--------|--------|--------|

| 4.4.3QSR1                  | Х         | Х       | X       | X      | Х      |        |

| 4.4.5                      | Х         |         | Х       | Х      | Х      | Х      |

| 4.4.6                      | Х         |         | Х       |        | Х      | Х      |

Table 2-2. Supported Platforms

#### **License Requirements**

In addition to your standard Advanced Design System licenses, the following additional product licenses are required.

#### **RFIC Dynamic Link License**

- trans\_idf (for ADS 2002)

- Idf\_c\_interface ( previous ADS Dynamic Link Versions)

#### **Cadence Licenses**

- OASIS\_Simulation\_Interface

- 34510 Affirma(TM) analog design environment

- 300 Virtuoso(R) layout editor (if using layout)

**Note** You must purchase all required Cadence licenses from Cadence Design Systems.

### Installing RFIC Dynamic Link

The RFIC Dynamic Link installation procedure continues to be improved to make it easier for you to install and configure.

To install RFIC Dynamic Link:

- 1. Follow instructions in the ADS *"Installation on UNIX Systems"* manual to run the SETUP utility and load the *install* program.

- 2. After the *Agilent EEsof Installation Manager* starts, you are prompted to select one of the following installation options:

- **Typical** If you choose a *Typical* installation, the *RFIC Dynamic Link* will not be installed.

- **Complete** If you choose a *Complete* installation, the RFIC Dynamic Link will be automatically installed.

- **Custom** If you choose a *Custom* installation, you must select both *Simulators and Design Entry* and *The RFIC Dynamic Link* components from the scroll-down list in the *Agilent EEsof Software Installation* dialog box.

**Note** The *Simulators and Design Entry* component is the basic ADS software, including the Design Environment, Data Display, and Analog/RF Systems and Signal Processing simulators. This is a minimum requirement for RFIC Dynamic Link.

| Agilent EEsof Software Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ۱                                                                                 |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|--|--|--|--|

| Welcome Platforms Setup Components Options                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Summary Install                                                                   |  |  |  |  |  |

| Select the Components from the list below which you would like to<br>system. Make sure you have enough disk space to install all the co<br>Use the Scroll bar to select additional components from the list.<br>After you have selected the desired components, click the Next bu<br>Click the 'Description' button for a more detailed description of eac<br>Previously installed components are marked by a small blue icon to<br>component checkbox. This does not, however, prevent reinstallation | imponents you select.<br>tton.<br>h component.<br>i the left of the corresponding |  |  |  |  |  |

| □ FLEXIm licensing software : 14160 KBytes       Description         ▲       ▼ The RFIC Dynamic Link : 13968 KBytes       Description         ▲       □ The Design Kit Tool Set : 1242 KBytes       Description                                                                                                                                                                                                                                                                                        |                                                                                   |  |  |  |  |  |

| – Component Description –                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                   |  |  |  |  |  |

| This component includes the RFIC Dynamic Link.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                   |  |  |  |  |  |

| Disk Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                   |  |  |  |  |  |

| Destination Directory: /hfs/d1/local/users/crscott/ADS200                                                                                                                                                                                                                                                                                                                                                                                                                                              | Destination Directory: /hfs/d1/local/users/crscott/ADS2002                        |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | KBytes                                                                            |  |  |  |  |  |

| Disk Space Available: 3917686                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | KBytes                                                                            |  |  |  |  |  |

| < Back Next >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Cancel Help                                                                       |  |  |  |  |  |

3. After the installation is complete, you will need to run the *idfConfigCadence* script to configure Cadence for use with RFIC Dynamic Link. This script is located under:

\$HPEESOF\_DIR/bin/idfConfigCadence

**Note** For ADS 2001, the Cadence configuration script was located at \$HPEESOF\_DIR/idf/config/configCadence.

For more information on the *idfConfigCadence* script, refer to "Running the idfConfigCadence Script" on page 2-6.

For more information on installation procedures, refer to the ADS *"Installation on UNIX Systems"* manual.

### **Configuring the Cadence Install Directory**

After the installation procedure (see "Installing RFIC Dynamic Link" on page 2-3), you will need to run the *idfConfigCadence* script. This script configures the Cadence install directory for use with ADS by adding or modifying five files.

Note You must have write access to your Cadence install directory.

The following four files are created:

```

<Cadence Installation Dir>/tools/dfII/etc/tools/ads/.cdsenv

<Cadence Installation Dir>/share/cdssetup/hierEditor/ads

<Cadence Installation Dir>/tools/dfII/etc/skill/hnl/ads.ile

<Cadence Installation Dir>/tools/dfII/etc/skill/si/caplib/ads.ile

```

**Note** For Cadence versions 4.4.5 & 4.4.6, the second line above is replaced by: <Cadence Installation Dir>/share/cdssetup/hierEditor/templates/ads

The fifth file, *<Cadence Installation Dir>*/tools/dfII/etc/tools/auCore/.cdsenv, is edited to add *ads* to the Tool Filter list of simulators.

**Note** The files described in this section are created or modified based on detailed instructions provided in the Cadence *OASIS Integrator's Guide*. The information in the Cadence manual describes how to integrate a simulator into Cadence *Analog Artist* using the Cadence *direct toolkit*.

**Important** While deviating from the information described in the Cadence *OASIS Integrator's Guide* may work for RIFC Dynamic Link, the files have been specifically set up to follow the Cadence documentation. Agilent Technologies does not support deviations from this information. For more information, refer to: Cadence OASIS Integrator's Guide

Version 4.4.5, December, 1999 Pages 4-12, 4-13, 6-2 and 6-6.

#### .

#### Running the idfConfigCadence Script

Before running the *idfConfigCadence* script, set HPEESOF\_DIR to your ADS installation directory and set your PATH to include Cadence software.

The *idfConfigCadence* command uses the following general syntax:

idfConfigCadence {-h | -ls | -rm}

Simply entering *idfConfigCadence* at the command line with no options runs the script to configure Cadence for RFIC Dyanmic Link. Table 2-3 displays a list of the options and definitions used by the *idfConfigCadence* command.

| Option | Definition                                                                                                                                                                                                                                                                              |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -h     | This option can be used to display the idfConfigCadence help file.                                                                                                                                                                                                                      |

| -ls    | This option can be used to list the Cadence configuration files for ADS/RFIC Dynamic Link and indicate whether Cadence is ready for ADS RFIC Dynamic Link or not.                                                                                                                       |

| -rm    | This option removes the Cadence configuration for ads/RFIC Dyanmic Link by deleting the files previously installed with the idfConfigCadence script and removing ads from the Cadence toolFilter. For more information on the Cadence Tool Filter, refer to your Cadence documentation. |

Table 2-3. Option Definitions for idfConfigCadence

#### Understanding the idfConfigCadence Script

When the *idfConfigCadence* script is executed without any options, the script performs the following operations:

Copies

\$HPEESOF\_DIR/idf/skill/4.4.X/adsCdsenvFile

to

<Cadence Installation Dir>/tools/dfII/etc/tools/ads/.cdsenv

• Copies

\$HPEESOF\_DIR/idf/config/ads.hierEd

to

<Cadence Installation Dir>/share/cdssetup/hierEditor/ads

• Creates two new empty files called *ads.ile* in the following locations:

<Cadence Installation Dir>/tools/dfII/etc/skill/hnl/ads.ile <Cadence Installation Dir>/tools/dfII/etc/skill/si/caplib/ads.ile

#### **Configuring for a New Cadence Release**

The *idfConfigCadence* script configures the Cadence installation directory for use with Dynamic Link. However, if a new version of the Cadence software is subsequently installed in a new directory, it will not have the Dynamic Link configuration. In this case, you would have to run the *idfConfigCadence* script as described in "Configuring the Cadence Install Directory" on page 2-5.

### **Configuring the Software**

This section describes the various aspects of configuring and/or modifying the software to provide additional flexibility.

#### **Configuring the UNIX Environment**

There are several UNIX environment variables relevant to Dynamic Link. These are described in the table below:

| Environment Variable | Description                                                                                                                                                                                  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IDF_CONFIG_FILE      | The name of the configuration file (only the file name, not the entire path). Default value is <i>idf.cfg.</i>                                                                               |

| IDF_ADS_PROJ_DIR     | If this environment variable is defined, ADS will attach to the specified project when RFIC Dyanmic Link launces ADS.                                                                        |

| IDF_DEBUG_MODE       | If set to TRUE debugging will be turned on and additional log messages will be written to the CIW; the log files <i>mps.log</i> and <i>emx.log</i> are also created. Default value is FALSE. |

| IDF_LOG_FILE         | Name of the file (only the file name, not the entire path) to which ADS messages, normally written to <i>stderr</i> are redirected. Default value is <i>idf.log</i> .                        |

| PATH                 | The UNIX path variable.                                                                                                                                                                      |

Table 2-4. UNIX Environment Variables

#### **Configuring the ADS Install Directory**

The installation procedure configures the ADS install directory by automatically adding, modifying or replacing some files and/or directories.

The following files and/or directories are created, modified or replaced:

```

$HPEESOF_DIR/bin/idfmp

$HPEESOF_DIR/bin/idf

$HPEESOF_DIR/bin/idfConfigCadence

$HPEESOF_DIR/idf

$HPEESOF_DIR/idf/cdslib

$HPEESOF_DIR/idf/config

$HPEESOF_DIR/idf/config

$HPEESOF_DIR/idf/examples

$HPEESOF_DIR/idf/skill

$HPEESOF_DIR/idf/symbols

$HPEESOF_DIR/circuit/symbols/idfSymbol.dsn

$HPEESOF_DIR/config

$HPEESOF_DIR/config

$HPEESOF_DIR/config

$HPEESOF_DIR/config/ADSlibconfig

$HPEESOF_DIR/config/aDSlibconfig/aDSlibconfig

$HPEESOF_DIR/config/aDSlibconfig/a

```

#### Modifying the RFIC Dyanmic Link-Cadence Initialization File

The RFIC Dynamic Link-Cadence initialization file (*.cdsinit*) is located in the directory *\$HPEESOF\_DIR/idf/config/.cdsinit*. Append it to or load it from the first available .cdsinit file from the list below:

- <*Cadence Installation Dir>*/tools/dfII/local/.cdsinit

- ./.cdsinit

earlier files:

• \$HOME/.cdsinit

#### Modifying the Configuration File

Dynamic Link comes with the default configuration file *SHPEESOF\_DIR/idf/config/idf.cfg*. This file is used to set various site-specific or user-specific options. It is searched for and read sequentially from the following locations in the order given, so that settings in files read later override those of

```

$HPEESOF_DIR/idf/config/

$HOME/hpeesof/config/

./

```

The name of the configuration file can be set via the UNIX environment variable IDF\_CONFIG\_FILE. By default the configuration file is named *idf.cfg*.

The configuration file consists of lines in the form *<parameter> = <value>*. The various parameters that can be set in the configuration file are listed below, with brief descriptions and an example for each. If no configuration file is found or some parameters are not set, internal default values are used. Note that wherever a file name is required for a configuration parameter value, it may be specified with a path prefix that is a UNIX environment variable value or using standard UNIX conventions such as ~. A complete example configuration file can be found at the end of this section.

• **Model Path:** This is a space-separated list of directories that is searched in sequence until a model file for each implemented component is found. The default is ~/models. Example:

IDF\_MODEL\_PATH = "~/models /usr/local/eda/cmos/models"

Note This applies to Cadence IC 4.4.3 only.

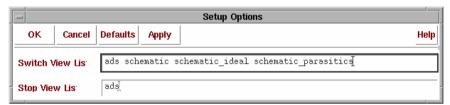

• **Switch View List:** If an instance has none of the views listed in the switch view list, the netlister reports an error. The default is *ads sch.model schematic*. Example:

IDF\_SWITCH\_VIEW\_LIST = "ads sch.model schematic"

• **Stop View List:** The netlister identifies primitives with a stop list. When it reaches a view that is listed in both the switch view and stop view lists, the instance is netlisted and no expansion occurs below this level. There is normally no reason to change the Stop View list to anything other than *ads*. Example:

IDF\_STOP\_VIEW\_LIST = "ads"

• **Project Path:** This indicates the path to the ADS project to attach to upon starting ADS via RFIC Dynamic Link. Example:

IDF\_ADS\_PROJ\_DIR = /tmp/ads\_prj

• **Netlist Filter:** When you have site customization that is not performed by the supplied netlister, this option enables you to specify the name of the program or script used to post-process the netlist generated by Analog Artist. The position of the netlist file name in your command string is indicated by %s. Example:

IDF\_NETLIST\_FILTER = "\$HPEESOF\_DIR/bin/myfilter %s"

• **Netlist Suffix:** This is the suffix for the Advanced Design System netlist file generated by Analog Artist for each sub-circuit. The default is *.net*. Example:

```

IDF_NETLIST_SUFFIX = ".net"

```

• **Model Suffix:** This is the suffix for each Advanced Design System model file in the specified model search path directories. The default is *.ads.* Example:

IDF\_MODEL\_SUFFIX = ".ads"

Note This applies to Cadence IC 4.4.3 only.

• **Debug Mode:** This option enables you to turn debugging messages on or off. These messages appear in order to help you determine the cause and/or location of problems.

By default, debugging is turned off. To enable debugging, set this option to  $\ensuremath{\textit{TRUE}}$  . Example:

IDF\_DEBUG\_MODE = TRUE

• **Symbol Generation:** This option enables you to specify whether to generate a missing symbol using the Cadence symbol generator or the Advanced Design System symbol generator. The Cadence symbol generator is used as the default. Example:

IDF\_CADENCE\_SYMBOL = FALSE

• **User AEL Files:** Users can define their own AEL functions and load them into the ADS environment via a list of comma separated file names. These files get loaded just after the Dynamic Link environment is initialized. Example:

IDF\_USER\_AEL\_FILES = "file1.ael, \$HOME/file2.atf"

• **Expression Mapping:** This causes sub-strings in Cadence expressions to be mapped to corresponding sub-strings in ADS expressions in the netlist file and/or in the design variable values used. Example:

IDF\_EXPR\_MAP = "foo bar"

• **Freezing Subcircuit Netlists:** When this variable is set to *yes* (or TRUE), all Cadence subcircuits for which a netlist already exists are not re-netlisted. The default is *FALSE*. Example:

IDF\_FREEZE\_NETLISTS = TRUE

Note The Freeze parameter can be set to yes(TRUE) or no (FALSE).

To freeze selected subcircuits, see "Freezing Selected Subcircuits" on page 9-10.

• **Message Timeout:** This specifies the timeout period in seconds for message actions initiated in ADS to complete in DFII. The default is 45. Example:

IDF\_MSG\_TIMEOUT = 120

• Other Options: The following special options should not be altered.

IDF\_AEL\_FILES = "globals.atf, utils.atf, commands.atf, callbacks.atf, symbol.atf, include.atf" IDF\_PDE\_EXEC = hpeesofde IDF\_PDE\_ARGS = "-env de\_sim" IDF\_PRODUCT\_NAME = idf IDF\_SCALE\_FACTOR = 2.0

#### **Example Configuration File**

```

IDF_MODEL_PATH = "~/models $HOME/myModels"

IDF_SWITCH_VIEW_LIST = "ads sch.model schematic"

IDF_ADS_PROJ_DIR = "./examples_prj"

IDF_NETLIST_FILTER = "~/bin/mynetlistfilter"

IDF_NETLIST_SUFFIX = ".net"

IDF_MODEL_SUFFIX = ".ads"

```

#### Modifying the BindKey Settings

When using Composer, the Dynamic Link bindkey settings are inherited from the Cadence *Schematics* application, just as happens for the *analogArtist-Schematic* application. This is the default or preferred behavior however, if custom bindkeys are required:

1. Modify the IdfSetBindKeys() function accordingly. This function is provided in the file:

\$HPEESOF\_DIR/idf/skill/bindKeys.il

For example, if you would like to modify your key mappings to match the ADS key mappings because you are more familiar with ADS, modify the bindkeys as described above.

2. Edit the *ads.ini* file replacing the call to the function, hilnheritBindKey("*IdfSchematic*" "*Schematics*") with a call to IdfSetBindKeys(). The *ads.ini* file is located in:

\$HPEESOF\_DIR/idf/skill/4.4.x/ads.ini

### **Managing Projects and Designs**

Your Cadence designs will remain in their original locations. They are not copied, translated, or otherwise modified. When ADS starts up in Dynamic Link mode, it puts you in a project directory defined by the IDF\_ADS\_PROJ\_DIR environment variable. If this variable is not defined, only the ADS Main window will open and no project will be attached.

To change this behavior, you can do one of the following:

• Specify your own startup project directory by defining IDF\_ADS\_PROJ\_DIR in your UNIX environment or via the configuration file *idf.cfg.*

• After the Advanced Design System has come up, go to the Main window and open a new or existing project (File > New or File > Open).

For more information on projects and design files, refer to "*Managing Projects and Designs*" in the ADS *User's Guide*.

Administrative Tasks

# **Chapter 3: Getting Started Tutorial**

This tutorial steps you through the process of simulating a circuit using components from the Dynamic Link *analogLib* library. Other examples are also included to help you become familiar with the product.

Both the drop-down menus and icons are described to help familiarize you with the Advanced Design System environment.

### Setting up the Examples Directory

From any directory of your choice, enter:

```

cp -r $HPEESOF_DIR/idf/examples ./ cd examples

```

**Note** This must be done before attempting the Getting Started Tutorial. The *cds.lib* file under the examples directory defines libraries provided by Dynamic Link. The *.cdsinit* file under this directory loads the Dynamic Link *.cdsinit* file which then loads the context files required to run Dynamic Link.

### **Starting the Cadence Design Framework**

Ensure that you are in the examples directory then open Cadence by typing the appropriate command (typically *icms* or *msfb*). The Cadence *Command Interpreter Window* (CIW) appears.

| - icms - Log: /gfs/sr/learn3/d1/local/users/crscott/CDS.log                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          | •      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|

| File Tools Options Technology File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Help     | 1      |

| COPYRIGHT © 1992-2000 CADENCE DESIGN SYSTEMS INC. ALL RIGHTS RESERVED.<br>© 1992-2000 UNIX SYSTEMS Laboratories INC.,<br>Reproduced with permission.<br>This Cadence Design Systems program and online documentation are<br>proprietary/confidential information and may be disclosed/used only<br>as authorized in a license agreement controlling such use and disclosure.<br>RESTRICTED RIGHTS NOTICE (SHORT FORM)<br>Use/reproduction/disclosure is subject to restriction<br>set forth at FAR 1252.227-19 or its equivalent.<br>Program:<br>© (#)SCDS: icms.exe version 4.4.6 08/30/2000 11:37<br>Sub version:<br>Loading geView.cxt<br>Loading selectSv.cxt<br>Loading selectSv.cxt<br>Loading analog.cxt | (cds117) | D1) \$ |

| I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |        |

| mouse L: M: R:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |        |

| >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |        |

Figure 3-1. Cadence CIW Window

**Note** Non-standard or customized start-up scripts for Cadence Design Framework II may not be supported. If you have difficulties, contact your system administrator.

#### **Opening a Cadence Composer Schematic**

To open a schematic in Cadence Composer:

1. Choose File > Open from the Cadence CIW. The Open File dialog box appears.

| -         |         |               | Open File              |    |

|-----------|---------|---------------|------------------------|----|

| ок        | Cancel  | Defaults      | He                     | lp |

| Library N | lame e: | xamples 🗆     | Cell Name:             |    |

| Cell Nam  | P       | owerAmp       | LC_filter<br>PowerAmp  |    |

| View Nar  | ne sc   | hematic 🗆     | amp<br>bjt_sub         |    |

|           | E       | rowse         | buf<br>examples<br>inv |    |

| Mode      | ۲       | edit )read    | lna<br>mixer           |    |

| Library p |         | cott/examples | mutual<br>mwline       | ,  |

|           |         |               |                        | 17 |

- 2. Select examples from the Library Name drop-down list.

- 3. Click *PowerAmp* in the Cell Names list. This sets the Cell Name field to PowerAmp.

- 4. Select *schematic* from the View Name drop-down list if not already selected.

- 5. Select the *edit* Mode if not already selected.

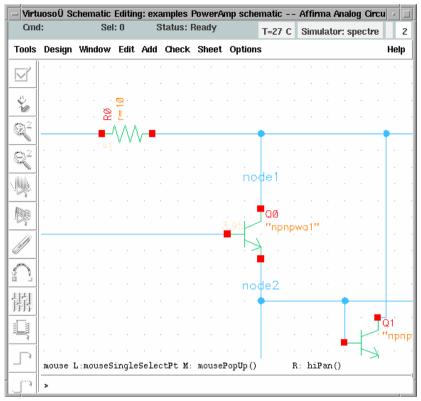

- 6. Click OK. The Cadence *examples, PowerAmp* schematic appears.

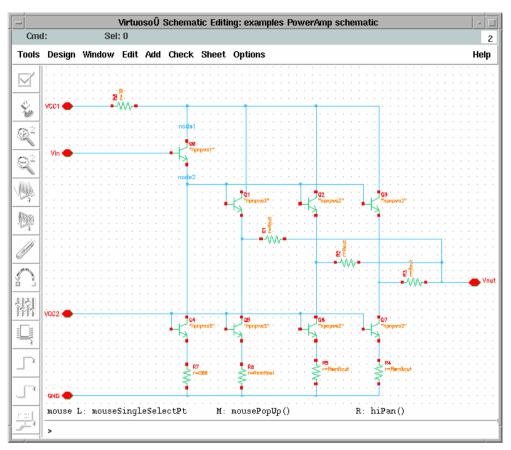

Figure 3-2. Cadence Virtuoso Schematic Composer Window

### Linking with Advanced Design System

To link the Cadence design environment to Advanced Design System:

1. Choose **Tools > ADS** from the menu bar in the Cadence Schematic window. In a few moments, the Advanced Design System Main window appears in the upper-left hand corner of your display. This is followed by an empty ADS Schematic window to the right of the Main window.

| - Advanced De                                  | sign System (Main)                                |

|------------------------------------------------|---------------------------------------------------|

| File View Options Window DesignKit De          | signGuide <u>H</u> elp                            |

| 🚰 🔗 🖬 🗞 💽 🔜 🖻                                  |                                                   |

| File Browser                                   | Project Hierarchy                                 |

| 📮 🗁 examples_prj                               | /hfs/d1/local/users/crscott/examples/examples_prj |

| <b>t</b>                                       |                                                   |

| Ē .nfs464                                      |                                                   |

| 🛛 🔤 🖃 arf_ful.rec                              |                                                   |

| E core                                         |                                                   |

| 🗌 🛶 🗄 data                                     |                                                   |

| 📄 🔤 de_sim.cfg                                 |                                                   |

| 🛛 🛏 🖻 dsp_ful.rec                              |                                                   |

| /hfs/d1/local/users/crscott/examples/examples_ | nj                                                |

Figure 3-3. Advanced Design System Main Window

**Note** Depending on your system, it may take a few moments for the ADS windows to appear. View the Cadence CIW window for the link status.

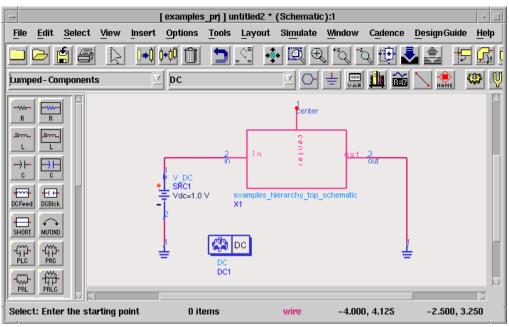

The ADS Schematic window should display a **Cadence** menu item and is automatically titled *untitled1* (see Figure 3-4).

|                                  | ADS      | S Schemat                 | ic Title              |          |          |

|----------------------------------|----------|---------------------------|-----------------------|----------|----------|

|                                  |          | C                         | adence Menu           | ı Item   |          |

|                                  |          |                           |                       |          |          |

| -                                |          | inples_prj   antilled1 (S |                       |          | <u> </u> |

|                                  |          |                           | w Cedence DesignChide |          | lleip    |

| 🖾 🎽 📓 🖄 🗎                        | 1 💷 🚊 🛄  | <u>ः</u> 🖺 र र            | A 🗄 🔜 A               | 🐜 👬 📈    |          |

| Lumped-Components                | 2        | 그아님!                      | 9) 🏨 📸 🟈 📐 🌸          | 🕸 🖖 🖂 🐺  | 5        |

|                                  |          |                           |                       |          | -<br>    |

| Select: Enter the starting point | 0 atomis | wre 6.                    | 625. 3.600            | III A/RE | SmSchem  |

Figure 3-4. Advanced Design System Schematic Window

At this point, ADS and the Cadence Design Framework II are working together.

### **Opening a Test Schematic Design**

To open a test schematic design:

1. Choose File > Open Design in the ADS Schematic window to display the Open Design dialog box. Use this dialog box to select the design you wish to simulate.

| -                                                                      | Open Design:1         |              |                |

|------------------------------------------------------------------------|-----------------------|--------------|----------------|

| Project                                                                |                       |              |                |

| examples_prj                                                           |                       | Ā            | Include/Remove |

| Filter                                                                 |                       |              |                |

| cal/users/crscott/exam                                                 | ples/examples_prj/net | works/*.dsn] | Browse         |

| — Open Design in: ———                                                  |                       |              |                |

| Current Window                                                         | 🔵 New Schematic Win   | dow 🔵 New    | Layout Window  |

| Designs                                                                |                       |              |                |

| examples_bjt_sub_schema<br>examples_PowerAmp_sche<br>PowerAmp_test.dsn |                       |              |                |

| * Design has been modified                                             | but not saved         |              |                |

| ΟΚ                                                                     | Filter                | ancel        | Help           |

- 2. The *examples\_prj* selection in the Project drop-down list is set by default in the Open Design dialog box.

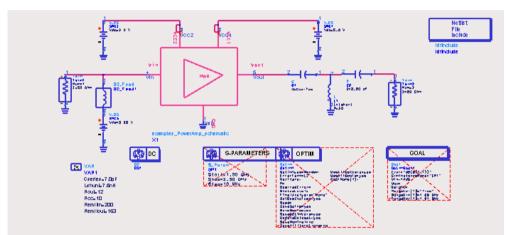

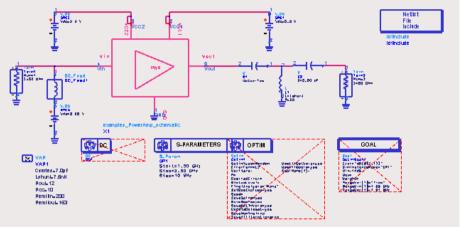

- 3. Select *PowerAmp\_test.dsn* from the Designs list. The *PowerAmp\_test.dsn* schematic contains simulation components that can be selectively activated or deactivated.

- 4. Click **OK** to include the *PowerAmp\_test.dsn* schematic in the ADS Schematic window.

### Adding a Symbol of the Cadence Cellview

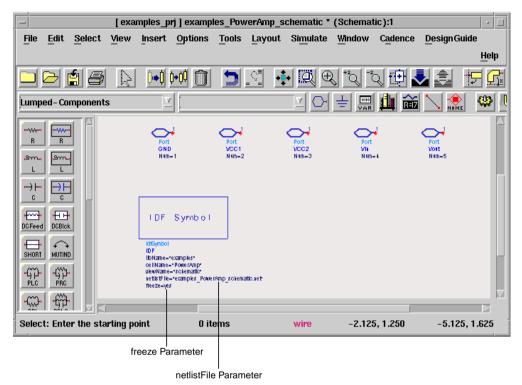

To add a symbol of the Cadence cellview in the Advanced Design System Schematic window:

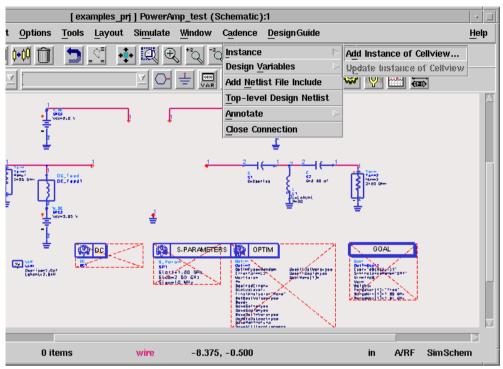

1. Choose Cadence > Instance >Add Instance of Cellview in the ADS Schematic window.

Figure 3-5. Adding a Cellview

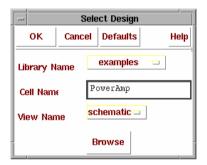

A Select Design dialog box appears, enabling you to select the Cadence Cellview to simulate.

| - Select Design       |                 |          |      |  |

|-----------------------|-----------------|----------|------|--|

| ок                    | Cancel Defaults |          | Help |  |

| Library N             | lame 🗌          | examples |      |  |

| Cell Name PowerAmp    |                 |          |      |  |

| View Name schematic - |                 |          |      |  |

|                       | B               | rowse    |      |  |

- 2. In the *Cell Name* field of this dialog, verify the entry or type the name of the Cellview you want to simulate (in this case *PowerAmp*). Alternatively, you can use the *Browse* button and library manager to select the name.

- 3. Click OK. A symbol of your Cadence Cellview is automatically generated.

- 4. An instance of the symbol is attached to the cursor for you to place. In the Advanced Design System Schematic window, click the left mouse button to place the symbol as desired.

- 5. You may continue placing more instances of the same cellview, or, in this case, choose the *Cancel Command And Return To Select Mode* icon to proceed with the next step. Similarly, you may place instances of other Cadence designs.

### **Adding Design Variables**

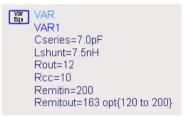

To add the design variables from the Cadence Cellview to the ADS schematic window choose Cadence > Design Variables > Get Design Variables.

This places a corresponding *VarEqn* component on the ADS schematic containing the design variables from Cadence (i.e. Rcc, Rout, Remitin and Remitout).

### Adding Model Files

To add a model file

- 1. Choose Cadence > Add Netlist File Include

- 2. Place the Netlist File Include component in an open area on the schematic.

- 3. Double click the include component icon. The *Netlist File Include* dialog box appears.

| N                                                                                                                          | letlist File Include                                  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|

| idfInclude<br>Instance Name<br>idfInclude                                                                                  |                                                       |  |  |  |

| Select Parameter<br>include Path=<br>definition Files=<br>stimulus Files=<br>modelLibrary Files[1]=<br>UsePreprocessor=yes | Model Library File Browse                             |  |  |  |

|                                                                                                                            | Section (optional)                                    |  |  |  |

| Add Cirit Paste                                                                                                            | ☐ Display parameter on schematic<br>Component Options |  |  |  |

| modelLibraryFiles : Model Library Files                                                                                    |                                                       |  |  |  |

| ОК Арріу                                                                                                                   | Cancel Reset Help                                     |  |  |  |

- 4. In the Netlist File Include dialog box, click **modelLibraryFiles** in the Select Parameter list box. The *Model Library File* field appears in the dialog box.

- 5. Click **Browse** just below the *Model Library File* field to locate the first model library file. The Select File dialog box appears.

| -                                                                                                                                                                                                                   | Select File:1                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

|                                                                                                                                                                                                                     | Filter<br>:/crscott/examples/models/* |

| Directories Files       Kamples/models/     Files       xamples/models/     npn1.ads       npnpwa1.ads     npnpwa2.ads       npnsub.ads     parms.inc       pjfet1.ads     pmesfet1.ads       pmos.ads     pmos.ads |                                       |

|                                                                                                                                                                                                                     | Selection                             |

|                                                                                                                                                                                                                     | OK Filter Cancel Help                 |

6. In the Select File dialog box, use the *Directories* field to locate the *models* directory.

<your\_current\_working\_dir>/examples/models

This sets the path for the location of the model library files.

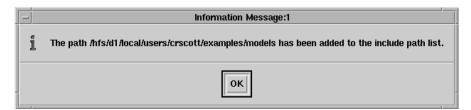

7. In the Select File dialog box, use the *Files* field to locate and click the **npnpwa1.ads** model file, then click **OK**. An information message appears stating that a new path has been added to the include path list.

Click **OK** in the *Information Message* dialog box. You are returned to the Netlist File Include dialog box.

- **8**. In the Netlist File Include dialog box, notice that the Model Library File field now contains the *npnpwa1.ads* model file. Click **Apply** to add the *npnpwa1.ads* model file.

- 9. Click **Browse** again to locate the second model library file. The Select File dialog box appears.

- In the Select File dialog box, use the *Files* field to locate and click the npnpwa2.ads model file, then click OK. You are returned to the Netlist File Include dialog box.

- 11. In the Netlist File Include dialog box, notice that the Model Library File field now contains the *npnpwa2.ads* model file. Click **Add** to add the *npnpwa2.ads* model file.

- 12. The Select Parameter field should now contain the information below.

modelLibraryFiles[1]=npnpwa1.ads

modelLibraryFiles[2]=npnpwa2.ads.

13. Click **OK** in the Netlist File Include dialog box.

For more information on the Netlist File Include Component, refer to "Using the Netlist File Include Component" on page 9-1.

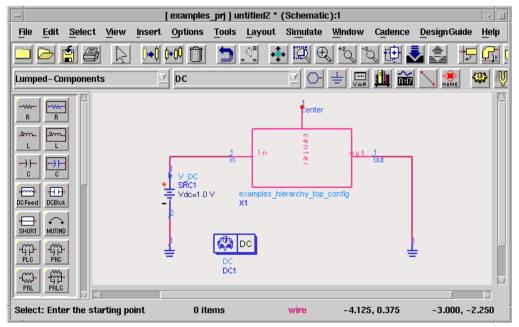

#### Performing a DC Simulation

To run a DC simulation on an ADS schematic and then annotate the results to the Cadence Composer Window:

1. Choose Edit > Component > Activate then click on the DC component in the ADS Schematic window or choose the *Activate Components* icon to activate the DC component.

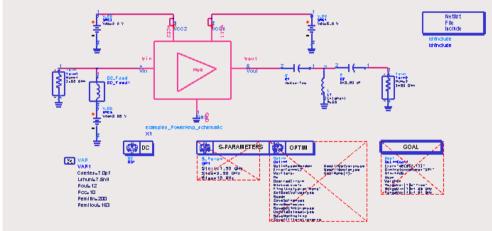

Figure 3-6. Activating Components in an ADS Schematic Window

2. Choose **Simulate > Simulate** or choose the *Simulate* icon to run a simulation. A simulation dialog box appears in your display.

| -        | hpeesofsim -31595:0 🔹 🗆                                                                                         |

|----------|-----------------------------------------------------------------------------------------------------------------|

| File     | Simulation/Synthesis Text Window                                                                                |

| Simul    | ation / Synthesis Messages                                                                                      |

| <b>-</b> |                                                                                                                 |

| i i      | i                                                                                                               |

|          |                                                                                                                 |

| 6        | i                                                                                                               |

| Ľ        | !                                                                                                               |

| Statu    | us / Summary                                                                                                    |

|          | A                                                                                                               |

| Conv     | ergence achieved in 7 iterations.                                                                               |

|          |                                                                                                                 |

|          | lation finished: dataset `PowerAmp_test´ written in:<br>hfs/d1/local/users/crscott/examples/examples_prj/data´. |

|          |                                                                                                                 |

|          | urce usage:<br>Total stopwatch time: 2.18 seconds.                                                              |

|          |                                                                                                                 |

|          |                                                                                                                 |

|          |                                                                                                                 |

- 3. After the simulation is complete, a Data Display window titled *PowerAmp\_test* automatically appears. Close this window using the File > Close Window menu option.

- 4. Click the PowerAmp schematic symbol in the ADS Schematic window.

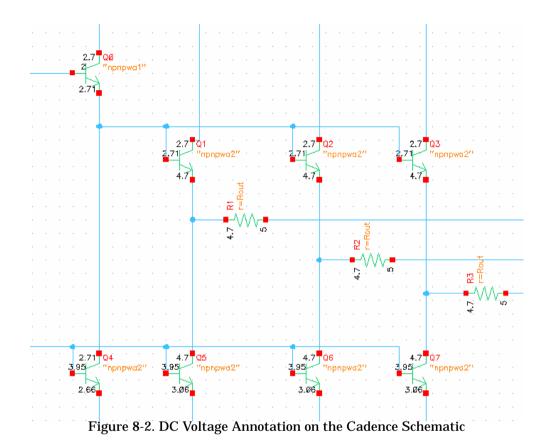

- 5. Choose Cadence > Annotate > Annotate DC Solution to Selected Cellview. This displays the DC node voltages on the Cadence schematic.

Figure 3-7. Cadence Schematic with Annotated Display

## Annotating DC Operating Points to a Selected Cellview

Any simulation that includes a DC analysis produces DC operating point information for most active and some passive devices in the circuit. This data includes currents, power, voltages, and linearized device parameters of the selected device.

To run a DC Operating Point Simulation on an ADS schematic and then annotate the results to the Cadence Composer Window:

1. Double-click the DC Simulation component in the ADS schematic window. The DC Operating Point Simulation dialog box appears.

| -          | DC Operating Point Simulation:1 |           |         |  |  |  |  |  |

|------------|---------------------------------|-----------|---------|--|--|--|--|--|

| DC Instanc | DC Instance Name                |           |         |  |  |  |  |  |

| þc1        |                                 |           |         |  |  |  |  |  |

| Sweep      | Parameters                      | Output    | Display |  |  |  |  |  |

|            |                                 |           |         |  |  |  |  |  |

|            |                                 |           |         |  |  |  |  |  |

|            |                                 |           |         |  |  |  |  |  |

| - Conve    | ergence                         |           |         |  |  |  |  |  |

| Max. D     | elta V 0.0                      | V Vo      | lts     |  |  |  |  |  |

| Max. It    | erations 250                    |           |         |  |  |  |  |  |

| Mode       | Auto seque                      | ence      | Ā       |  |  |  |  |  |

| - Levels   | s ———                           |           |         |  |  |  |  |  |

| Status     | level 2                         |           |         |  |  |  |  |  |

| Dovice     | e operating poin                | t lovol   |         |  |  |  |  |  |

|            |                                 |           |         |  |  |  |  |  |

| 🔿 Non      | e 📋 Brief                       | letail 🍈  | ed      |  |  |  |  |  |

| — Outpu    | t solutions ——                  |           |         |  |  |  |  |  |

| 🗆 Outp     | out solutions at                | all steps |         |  |  |  |  |  |

|            |                                 |           |         |  |  |  |  |  |

|            |                                 |           |         |  |  |  |  |  |

|            |                                 |           |         |  |  |  |  |  |

|            |                                 |           |         |  |  |  |  |  |

| ок         | Apply                           | Cancel    | Help    |  |  |  |  |  |

- 2. Click the Parameters tab in the DC Operating Point Simulation dialog box.

- 3. Click **Detailed** in the *Device operating point level* section of the DC Operating Point Simulation dialog box.

**Note** For a subset of the detailed DC Operating Point Simulation information that covers most common parameters, click **Brief** in the *Device operating point level* section of the DC Operating Point Simulation dialog box.

- 4. Choose Simulate > Simulate or choose the *Simulate* icon to run a simulation. A simulation dialog box appears in your display.

- 5. After the simulation is complete, a Data Display window titled *PowerAmp\_test* automatically appears. Close this window using the **File > Close Window** menu option.

- 6. Click the PowerAmp schematic symbol in the ADS Schematic window.

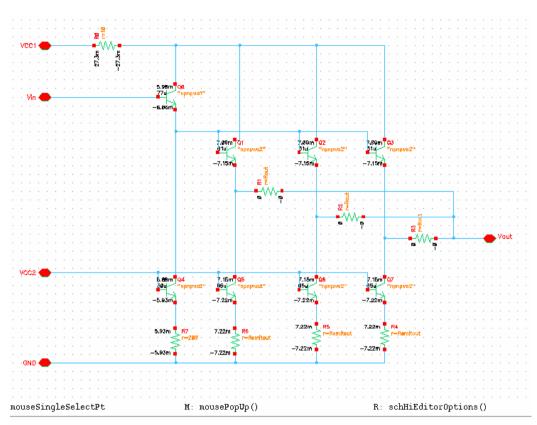

- 7. Choose Cadence > Annotate > Annotate Operating Points to Selected Cellview. This displays the DC operating point values for each component on the Cadence schematic.

#### Node Probing with RFIC Dynamic Link

With the RFIC Dynamic Link Node-Probing feature, you can select nodes of interest in a Cadence subcircuit and display their voltages in an ADS Data Display window. ADS saves voltage data for all the named nodes. Any node with a node name prefix different from *\_net* is considered a named node. For detailed information on the ADS Node-Probing feature, refer to the ADS *"Circuit Simulation"* manual.

The following is an example session of using the Dynamic Link Node-Probing feature with the PowerAmp example.

1. In the Cadence schematic window, choose **Options > Editors**. The Cadence *Editor Options* form appears.

| Edito                        | or Options                 | ]             |

|------------------------------|----------------------------|---------------|

| OK Cancel Defaults A         | pply Help                  |               |

| Command Control:             |                            | 1             |

| Add Instance Browser Type    | library component          |               |

| Block Pin Direction Rule     | ● edge _) order of entry   |               |

| Wire Snappinc                | 🔵 off 📵 on                 |               |

| Automatic Solder Dots        | 🔵 off 📵 on                 |               |

| Solder Dot Wire Overla;      | 0.03125                    |               |

| Symbol Generator Pin Sortinc | 🖲 alphanumeric 🔵 geometric |               |

| Add Symbol Pins as Instance: | (€ off _) on               |               |

| Modal Command:               | 🔵 off 🖲 on                 |               |

| Cross Selection              | (€ off _) on               |               |

| Gravity                      | 🔵 off 🖲 on                 |               |

| Minimum Marker Size          | 0.05                       |               |

| View Name Lis <sup>®</sup>   | ads sch.model schematic    |               |

| System Generated Net Name:   |                            |               |

| Bus Range Orde               | ascendingdescending        |               |

| Net Name Methoc              | prefixderived              |               |

| Ref Name Separato            | -                          |               |

| Net Name Prefix              | netį —                     | – Change to _ |

- 2. Change Net Name Prefix field from *net* to \_*net* then click **OK**. This prevents ADS from saving data for all the nodes in the PowerAmp cellview.

- 3. Click **Design > Check and Save** in the Cadence schematic window to ensure a new ADS netlist for the *PowerAmp* cellview is generated the next time a simulation is performed for the ADS *PowerAmp\_test* design.

- 4. Double click the DC Simulation controller component in the ADS schematic window to open the *DC Operating Point Simulation* dialog box.

| -                  | DC Operatino  | j Point Simul | ation:1   |  |  |  |  |  |

|--------------------|---------------|---------------|-----------|--|--|--|--|--|

| DC Instance Name   |               |               |           |  |  |  |  |  |

| þc1                |               |               |           |  |  |  |  |  |

| Sweep              | Parameters    | Output        | Display   |  |  |  |  |  |

| Save by hierarchy: |               |               |           |  |  |  |  |  |

|                    | ,             | Maxir         | num Depth |  |  |  |  |  |

| Nodo               | Voltages:     | incom         | 2         |  |  |  |  |  |

|                    | Ū             |               |           |  |  |  |  |  |

| 🗙 Meas             | urement Equat | tions:        | Ž         |  |  |  |  |  |

| - Save by          | name:         |               |           |  |  |  |  |  |

|                    |               |               |           |  |  |  |  |  |

|                    |               |               |           |  |  |  |  |  |

|                    |               |               |           |  |  |  |  |  |

|                    |               |               |           |  |  |  |  |  |

|                    |               |               |           |  |  |  |  |  |

|                    |               |               |           |  |  |  |  |  |

|                    |               |               |           |  |  |  |  |  |

|                    |               |               |           |  |  |  |  |  |

|                    |               |               |           |  |  |  |  |  |

|                    |               |               |           |  |  |  |  |  |

|                    | Add / Re      | emove         |           |  |  |  |  |  |

|                    |               |               |           |  |  |  |  |  |

| ОК                 | Apply         | Cancel        | Help      |  |  |  |  |  |

- 5. Click the **Output** tab in the *DC Operating Point Simulation* dialog box.

- 6. Click Add/Remove in the *Output* section of the *DC Operating Point Simulation* dialog box to open the *Edit OutputPlan* dialog box.

| -                                                                                         | Edit OutputPlan:1   | 1                  |

|-------------------------------------------------------------------------------------------|---------------------|--------------------|

| Available Outputs:<br>Nodes E Cseries E Lshunt E Recc E Remitunt E Remitout E Rout E Rout | Add >><br><< Remove | Current Selection: |

| ОК                                                                                        | Cancel              | Help               |

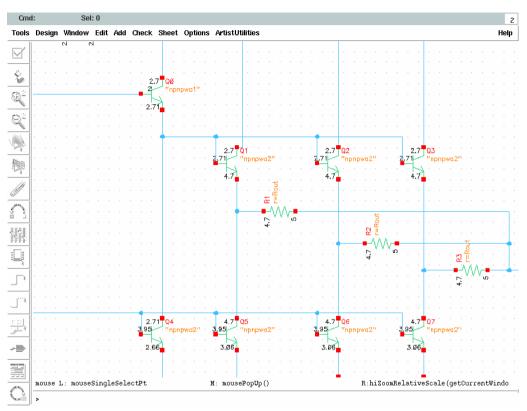

- 7. Click the + sign to the left of the X1 component in the *Available Outputs* field to start Dynamic Link Node Probing setup. This raises the Cadence schematic window containing the PowerAmp cellview. The prompt in the Cadence schematic window is changed to **ADS Node Probing Setup: Click a wire>**.

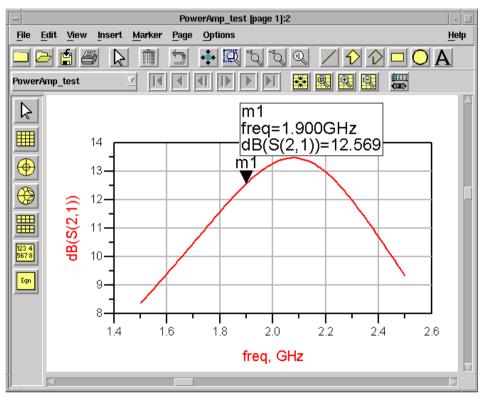

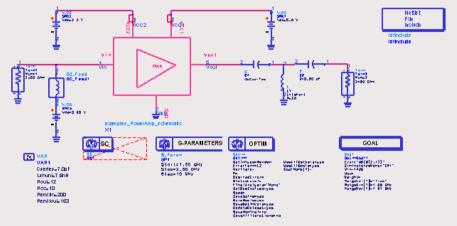

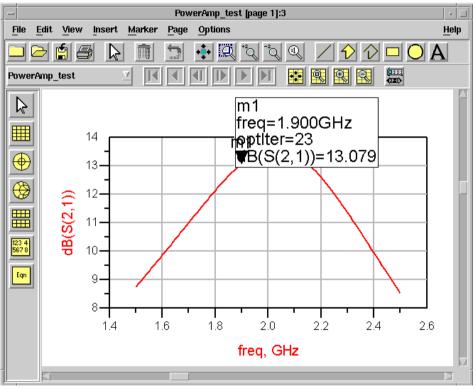

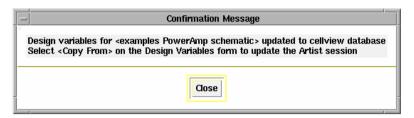

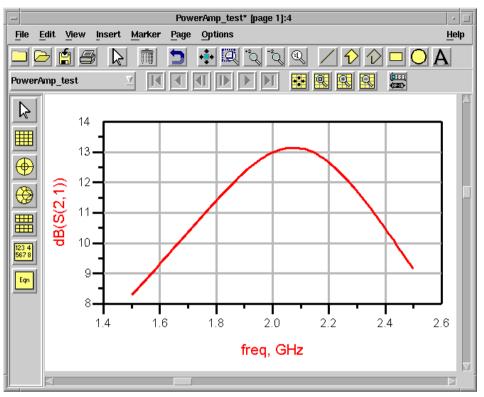

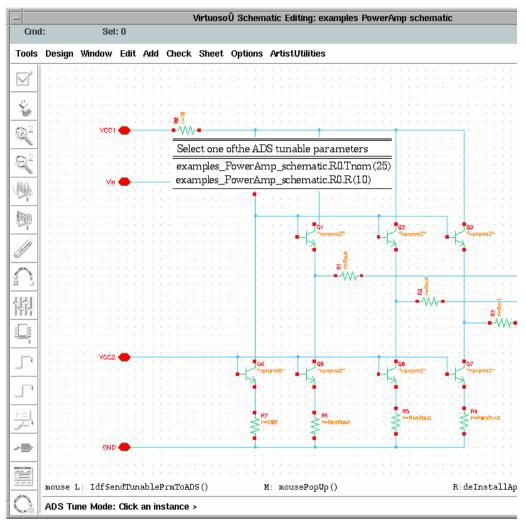

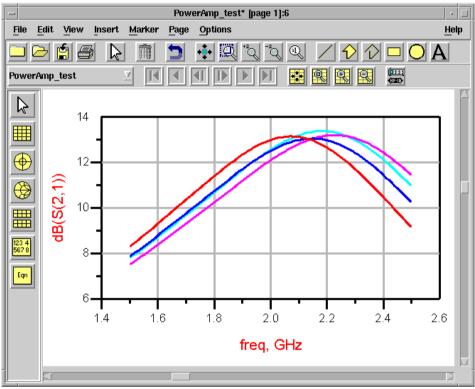

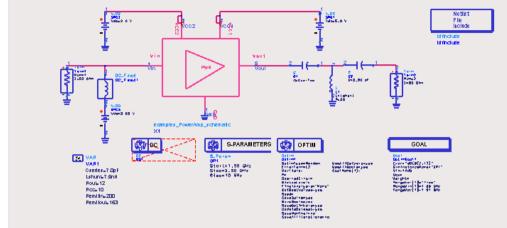

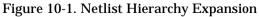

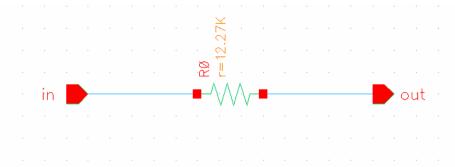

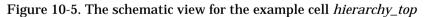

- 8. Click the wire connecting to the collector of the Q0 transistor in the upper-left region of the schematic window. A *node1* label is added to that wire in the Cadence schematic window. Meanwhile, *node1* also appears in the *Current Selection* field on the right side of the ADS *Edit OutputPlan* dialog box.